# Specification for

# QUAD SMALL FORM FACTOR PLUGGABLE MODULE 112

QSFP112 Published Specification Rev. 2.0

January 22, 2022

#### Abstract:

This specification defines the electrical connectors, electrical signals and power supplies, mechanical and thermal requirements of the QSFP112 module, connector and cage systems.

This document provides a common specification for system manufacturers, system integrators, and suppliers of modules.

#### **Points of Contact:**

| Co-chair         | Liang Chen, Alibaba  | Liang Chen at alibaba-inc.com  |

|------------------|----------------------|--------------------------------|

|                  | Die Wan, Baidu       | Die Wan at Baidu.com           |

|                  | Dayong Shen, Tencent | Dayong Shen at Tencent.com     |

| Technical editor | Vito Chen, Luxshare  | Vito Chen at Luxshare-ict.com  |

|                  | Zian He, InnoLight   | Zian He at InnoLight.com       |

|                  | Robert Luo, Luxshare | Robert Luo at Luxshare-ict.com |

|                  | Hai Ding, InnoLight  | Hai Ding at InnoLight.com      |

| Contact Email    | Contact@qsfp112.com  |                                |

#### **Promoter and Contributor:**

The list below summarizes representatives, including company of representatives, who provided initial feedback on the scope, content and presentation of draft versions of this document. Inclusion on this list does not indicate agreement with each specification line item or the document as a whole.

| Company  | Promoter or Contributor |

|----------|-------------------------|

| Accelink | Promoter                |

| Alibaba  | Promoter                |

| Amphenol | Promoter                |

| Baidu    | Promoter                |

| Credo    | Promoter                |

| H3C      | Promoter                |

| Hisense                              | Promoter    |

|--------------------------------------|-------------|

| Huaqin                               | Promoter    |

| II-VI                                | Promoter    |

| InnoLight                            | Promoter    |

| Inspur                               | Promoter    |

| JD                                   | Promoter    |

| Kuaishou                             | Promoter    |

| Luxshare                             | Promoter    |

| Marvell                              | Promoter    |

| Meituan                              | Promoter    |

| Molex                                | Promoter    |

| Ruijie                               | Promoter    |

| TE                                   | Promoter    |

| Tencent                              | Promoter    |

| US Conec                             | Promoter    |

| Applied<br>Optoelectronics Inc       | Contributor |

| ATOP                                 | Contributor |

| Broadex-Tech                         | Contributor |

| Color-chip                           | Contributor |

| Electric Connector<br>Technology Co. | Contributor |

| Eoptolink                            | Contributor |

| FIT                                  | Contributor |

| GLGNET                               | Contributor |

| Insiga                               | Contributor |

| Kingsignal                           | Contributor |

| Linktel                              | Contributor |

| Nvidia                               | Contributor |

| Shijia Photonics                     | Contributor |

| SiFotonics<br>Technologies           | Contributor |

| Source Photonics         | Contributor |

|--------------------------|-------------|

| Volex                    | Contributor |

| Xena Networks            | Contributor |

| Yuanjie<br>Semiconductor | Contributor |

| Zhaolong                 | Contributor |

Limitations on the Use of this Information:

This QSFP112 specification is provided "AS IS" with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warranty otherwise arising out of any proposal, specification or sample. The authors and promoters disclaim all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification. In no event shall the QSFP112 participants be liable for any direct, indirect, special, exemplary, punitive, or consequential damages, including, without limitation, lost profits, product liabilities, even if advised of the possibility of such damages.

This QSFP112 specification may contain or require the use of intellectual property owned by others. No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted herein, except that a license is hereby granted to download, reproduce and distribute this document under the provisions of the QSFP112 MSA.

# **Revision History**

| Revision | Date            | Release                        | Remarks                                                                                                                                                                                                                                                                                |  |  |

|----------|-----------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 1.0      | June 10, 2021   | 1 <sup>st</sup> public release |                                                                                                                                                                                                                                                                                        |  |  |

| 2.0      | January 22,2022 | 2 <sup>nd</sup> public release | <ul> <li>-Added chapter 5.9 for QSFP112 Qpath112 connector and cage definition.</li> <li>-Added Figure 18 and Figure 19 for QSFP112 Qpath112 2X1 connector and cage PCB layout.</li> <li>Updated Figure 17 and Figure 24 for QSFP112 2X1 SMT connector and cage PCB layout.</li> </ul> |  |  |

# TABLE OF CONTENTS

| 1 Scope                                                             | 10 |

|---------------------------------------------------------------------|----|

| 2 Reference                                                         | 10 |

| 3 QSFP112 Application Reference Examples                            | 11 |

| 4 Electrical Interface                                              | 12 |

| 4.1 Electrical Connector                                            | 12 |

| 4.1.1 Low Speed Electrical Hardware Pins                            | 16 |

| 4.1.2 Low Speed Electrical Specification                            | 17 |

| 4.1.3 High Speed Electrical Specification                           |    |

| 4.2 Power Requirements                                              | 19 |

| 4.2.1 Host Board Power Supply Filtering                             |    |

| 4.2.2 Power Classes and Maximum Power Consumption                   | 21 |

| 4.3 ESD                                                             | 23 |

| 5 Mechanical and Board Definition                                   | 23 |

| 5.1 Introduction                                                    | 23 |

| 5.2 QSFP112 Datums and Component Alignment                          | 23 |

| 5.3 QSFP112 Module Mechanical Package Dimensions                    | 26 |

| 5.3.1 Module Form Factors                                           |    |

| 5.3.2 Module Flatness and Roughness                                 | 29 |

| 5.3.3 Mating of QSFP112 Module PCB to QSFP112 Electrical Connector  | 29 |

| 5.4 Host PCB Layout                                                 | 30 |

| 5.4.1 Insertion, Extraction and Retention Forces for QSFP112 Module |    |

| 5.5 Module Color Coding and Labeling                                | 34 |

| 5.6 Bezel for Systems Using QSFP112 Modules                         | 34 |

| 5.7 QSFP112 Electrical Connector Mechanical                         | 35 |

| 5.8 QSFP112 Cage Assembly                                           | 37 |

| 5.8.1 QSFP112 Heatsink dimensions                                   |    |

| 5.9 QSFP112 Qpath112 Connector and cage                             | 38 |

| 5.10 Optical Port Mapping and Optical Interfaces                    | 40 |

| 5.10.1 Electrical data input/output to optical port mapping         | 40 |

| 5.10.2 Optical Interfaces                                           |    |

| 6 Environmental and Thermal                                         |    |

| 6.1 Temperature Classes                                             | 42 |

| 6.2 Informative Thermal Design                                      |    |

| 7 Management Interface                                              |    |

| 7.1 Introduction                                                    |    |

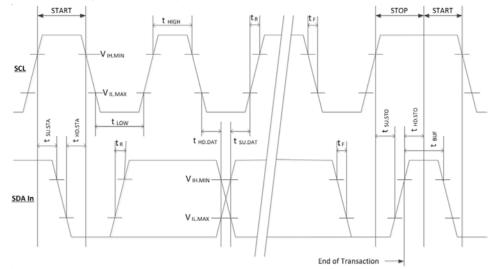

| 7.2 Timing Specification                                            |    |

| 7.2.1 Introduction                                                  |    |

| 7.2.2 Management Interface Timing Specification                     |    |

| 7.2.3 Serial Interface Protocol                                     |    |

| 7.3 Timing for Soft Control and Status Functions                    | 46 |

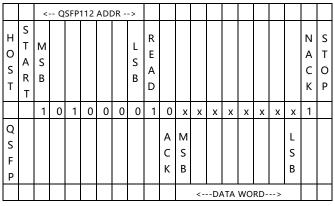

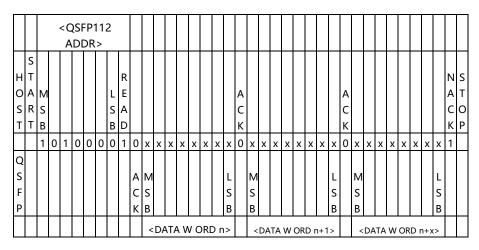

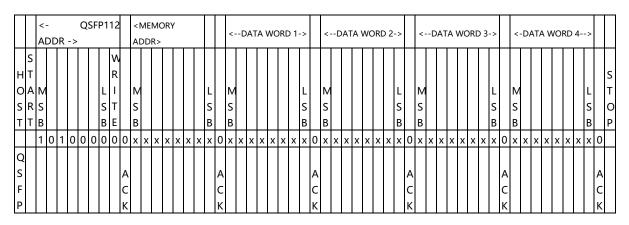

# QSFP112 Specification Rev. 2.0QSFPDD27.4 Device Addressing and Operation.487.5 Read/Write Functionality.497.5.1 QSFP112 Memory Address Counter (Read AND Write Operations).497.5.2 Read Operations (Current Address Read).497.5.3 Read Operations (Random Read).497.5.4 Write Operations (BYTE Write).517.5.5 Write Operations (Sequential Write)517.5.6 Write Operations (Acknowledge Polling).527.6 QSFP112 Memory Map52

#

# TABLE OF FIGURES

| Figure 1 Application reference model                                    | 11 |

|-------------------------------------------------------------------------|----|

| Figure 2 QSFP112 Module contact assignment                              | 12 |

| Figure 3 QSFP112 Host PCB pad assignment                                | 12 |

| Figure 4 Example QSFP112 host board schematic for optical modules       | 14 |

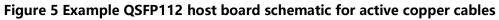

| Figure 5 Example QSFP112 host board schematic for active copper cables  | 15 |

| Figure 6 Example QSFP112 host board schematic for passive copper cables | 15 |

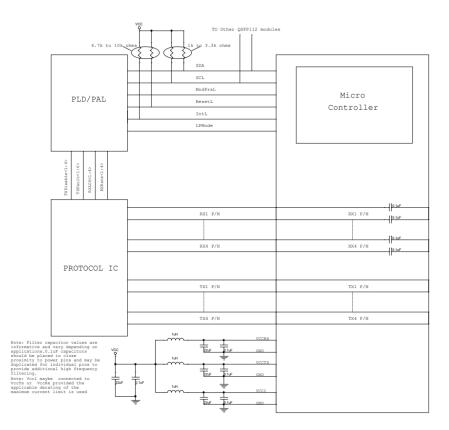

| Figure 7 Recommended host board power supply filtering                  | 20 |

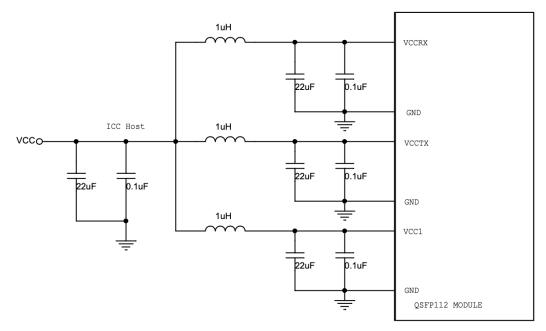

| Figure 8 Instantaneous and sustained peak currents for icc host         | 21 |

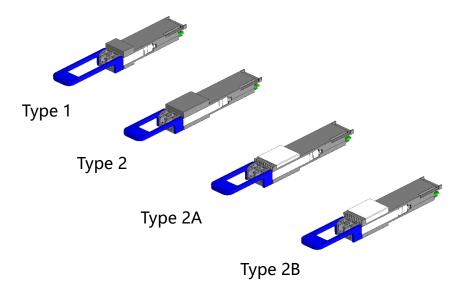

| Figure 9 QSFP112 Module rendering                                       |    |

| Figure 10 QSFP112 1X1 SMT Connector/Cage/Module Datum                   | 25 |

| Figure 11 QSFP112 2X1 SMT Connector/Cage/Module Datum                   | 25 |

| Figure 12 Drawing of QSFP112 module (Part 1 of 2)                       | 27 |

| Figure 13 Drawing of QSFP112 module (Part 2 of 2)                       |    |

| Figure 14 QSFP112 Improved paddle card dimensions                       | 29 |

| Figure 15 QSFP112 1x1 SMT Connector and cage PCB layout                 |    |

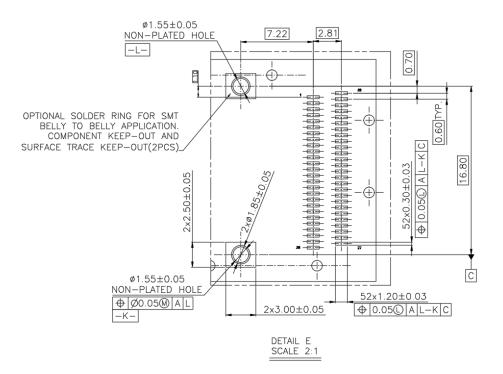

| Figure 16 QSFP112 1x1 SMT Connector and cage PCB layout, Detail E       |    |

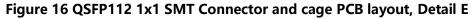

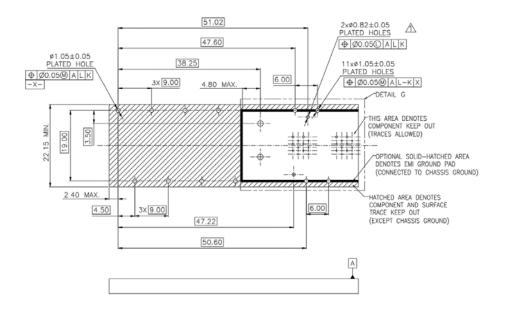

| Figure 17 QSFP112 2X1 SMT Connector and cage PCB layout                 |    |

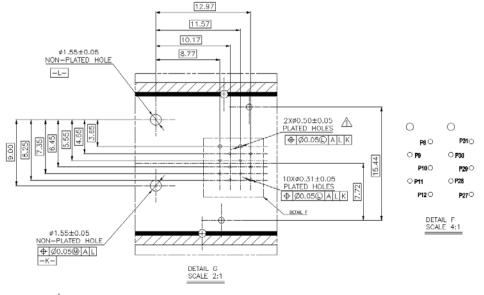

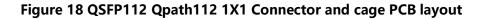

| Figure 18 QSFP112 Qpath112 1X1 Connector and cage PCB layout            |    |

| Figure 19 QSFP112 Qpath112 2X1 Connector and cage PCB layout            |    |

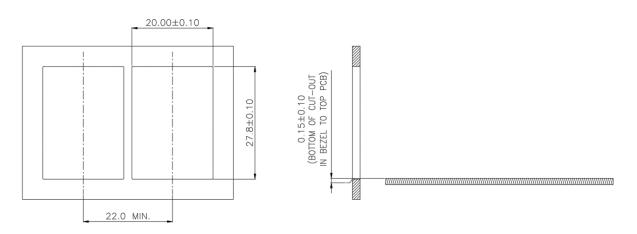

| Figure 20 QSFP112 1X1 SMT and Qpath112 Bezel opening                    |    |

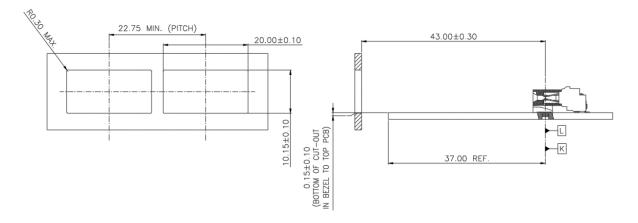

| Figure 21 QSFP112 2X1 SMT and Qpath112 Bezel opening                    |    |

| Figure 22 QSFP112 Module electrical connector illustration              |    |

| Figure 23 QSFP112 1X1 SMT Connector                                     |    |

| Figure 24 QSFP112 2X1 SMT Connector                                     |    |

| Figure 25 QSFP112 1x1 Cage                                              |    |

| Figure 26 QSFP112 2X1 Cage                                              |    |

| Figure 27 QSFP112 Heatsink                                              |    |

| Figure 28 QSFP112 Qpath112 1X1 Connector and cage illustration          |    |

| Figure 29 QSFP112 Qpath112 1X1 Connector and cage                       |    |

| Figure 30 QSFP112 Qpath112 2X1 Connector and cage illustration          |    |

| Figure 31 QSFP112 Qpath112 2X1 Connector and cage                       |    |

| Figure 32 Optical media dependent interface port assignments            |    |

| Figure 33 MPO-12 One row optical patch cord and module receptacle       | 41 |

| Figure 34 Dual LC optical patchcord and module receptacle               | 41 |

| Figure 35 QSFP112 Module variants: Type 1; Type 2; Type 2A; and Type 2B | 43 |

| Figure 36 TWI Timing diagram                                            |    |

| Figure 37 QSFP112 Device address                                        |    |

| Figure 38 QSFP112 Current address read operation                        |    |

| Figure 39 QSFP112 Random read                                           |    |

| Figure 40 Sequential address read starting at QSFP112 current address   | 50 |

| QSFP112 Specification Rev. 2.0                                       | QSFP112 |

|----------------------------------------------------------------------|---------|

| Figure 41 Sequential address read starting with random QSFP112 read. |         |

| Figure 42 QSFP112 Write byte operation                               |         |

| Figure 43 QSFP112 Sequential write operation                         |         |

| Figure 44 Type 2A and 2B examples of extruded Heat Sink Example      |         |

| Figure 45 Type 2A and 2B examples of die Cast Heat Sink Example      |         |

| Figure 46 Type 2A and 2B examples of zipper Fin Heat Sink Example    | 55      |

# LIST OF TABLES

| Table 1 Multimode fiber applications                                       | 11 |

|----------------------------------------------------------------------------|----|

| Table 2 Single mode fiber applications                                     | 11 |

| Table 3 QSFP112 Module contact and Host PCB pad electrical definition      | 13 |

| Table 4 Low speed control and sense signals                                | 18 |

| Table 5 Power supply specification                                         | 20 |

| Table 6 Power budget classification                                        | 21 |

| Table 7 QSFP112 Module power supply specification                          | 22 |

| Table 8 Definition of datums                                               | 24 |

| Table 9 QSFP112 Module flatness specifications                             | 29 |

| Table 10 Insertion, extraction and retention forces for an QSFP112 module  |    |

| Table 11 Electrical Signal to Optical Port Mapping                         | 40 |

| Table 12 (a) Temperature classification of module case                     | 42 |

| Table 12 (b) Temperature range classes for tighter controlled applications | 42 |

| Table 13 Identifier Values                                                 | 43 |

| Table 14 Management interface timing parameters                            | 45 |

| Table 15 I/O Timing for soft control and status functions                  | 46 |

| Table 16 I/O Timing for squelch and disable                                | 47 |

| Table 17 Informative Dimensions for QSFP112 Module Type 2A/2B              | 55 |

# **QSFP**[][]2

# 1 Scope

The scope of this specification covers the following items:

- The QSFP112 (4-channel, up to 112 Gbps per channel) transceiver module including mechanical form-factor, electrical interface, power specification, ect

- Host cage together with the host electrical connector mating with plug

- Electrical interface, including pin-out, data, control, power and ground signals

- Mechanical interface, including package outline, front panel and PCB layout requirements

- Thermal requirements and limitations, including heat-sink and airflow design

- Electrostatic discharge (ESD) requirements, and EMI requirements

- Software Management Interface.

# 2 Reference

- ANSI/ESDA/JEDEC JS-001-2014: Electrostatic Discharge Sensitivity Testing Human Body Model (HBM) - Component Level

- CMIS (Common Management Interface Specifications) 5.0, see http://www.qsfp-dd.com

- EN61000-4-2:2008: Electromagnetic compatibility (EMC)- Part 4-2: Testing and measurement techniques Electrostatic discharge immunity test

- IEEE P802.3ck<sup>™</sup>/D1.5 Draft Standard for Ethernet Amendment: Physical Layer Specifications and Management Parameters for 100 Gb/s, 200 Gb/s, and 400 Gb/s Electrical Interfaces Based on 100 Gb/s Signaling

- IEEE P802.3db<sup>™</sup>/D1.0 Draft Standard for Ethernet Amendment: Physical Layer Specifications and Management Parameters for 100 Gb/s, 200 Gb/s, and 400 Gb/s Operation over Optical Fiber using 100 Gb/s Signaling

- OIF CEI-112G-VSR-PAM4 draft, Rev. 2017.346.15

- QSFP-DD Hardware Specification Rev.6.0

- QSFP-DD800 Specification Rev.1.0

- SFF-8024 SFF Module Management Reference Code Tables, Rev. 4.7

- SFF-8661 Specification for QSFP+ 4X Module, Rev2.5

- SFF-8636 Specification for Management Interface for 4-lane Modules and Cables, Rev. 2.10a

- SFF-8662 Specification for QSFP+ 4X 28 Gb/s Connector (Style A), Rev 2.9

- SFF-8663 Specification for QSFP+ 28 Gb/s Cage (Style A), Rev 1.7

- SFF-8665 QSFP+ 4X 28 Gb/s Pluggable Transceiver Solution (QSFP28), Rev 1.9

- SFF-8679 QSFP28 4X Base Electrical Specification, Rev 1.8

- Telcordia GR-63-CORE, Issue 5, December 2017

Each Participant acknowledges the Specifications will provide a common solution for combined fourchannel fiber optic ports that support SONET/SDH and/or Ethernet and/or Fiber Channel specifications. This MSA encompasses module design(s) capable of supporting multimode and single mode applications for operation covering the transmission rates and distances noted below. Other standards covering higher data rates and/or longer distance options are not part of this agreement but may be supported. A QSFP112 module may support applications in Table 1 and Table 2 that are supplied for reference only.

| PMD type | Required operating range |  |

|----------|--------------------------|--|

|          | 0.5m to 30m for OM3      |  |

| VR       | 0.5m to 50m for OM4      |  |

|          | 0.5m to 50m for OM5      |  |

|          | 0.5m to 60m for OM3      |  |

| SR       | 0.5m to 100m for OM4     |  |

|          | 0.5m to 100m for OM5     |  |

#### **Table 1 Multimode fiber applications**

#### Table 2 Single mode fiber applications

| PMD type | Required operating range |

|----------|--------------------------|

| DR       | 2m to 500m               |

| FR       | 2m to 2km                |

| LR       | 2m to 10km               |

| ER       | 2m to 40km               |

| ZR       | 2m to 80km               |

# **3 QSFP112 Application Reference Examples**

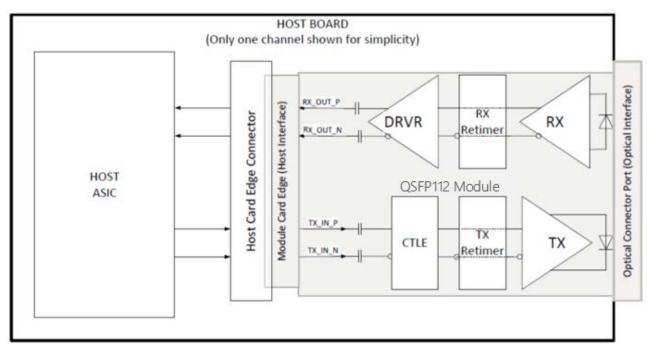

This specification defines a common four-lanes pluggable module that uses the following application reference Model. An Application Reference Model, shown in Figure 1, shows the high-speed data interface between an ASIC (SerDes) and the QSFP112 module.

#### Figure 1 Application reference model

# **QSFP**[][]2

# **4 Electrical Interface**

# **4.1 Electrical Connector**

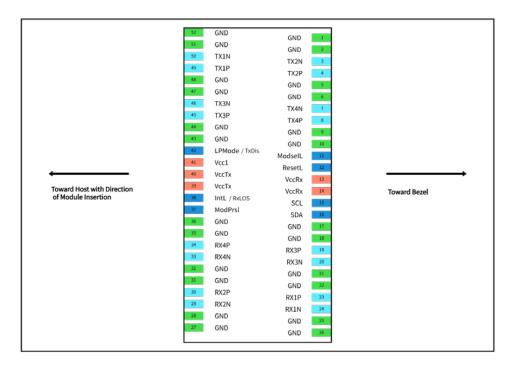

The QSFP112 connector is a 38-contact connector.

QSFP112 module contacts mate with the host in the order of ground, power, followed by signal as illustrated by Figure 2 and Figure 3 and the contact sequence order listed in Table 3.

| 38<br>37<br>36<br>35 | GND<br>TX1n<br>TX1p<br>GND | 7/                |                      | GND<br>TX2n<br>TX2p<br>GND | 1<br>2<br>3<br>4 |

|----------------------|----------------------------|-------------------|----------------------|----------------------------|------------------|

| 34                   | TX3n<br>TX3p               |                   |                      | TX4n                       | 5                |

| 32                   | GND                        |                   |                      | TX4p                       | 6                |

| 31                   | LPMode / TxDis             | $\langle \rangle$ | Mc                   | GND<br>odSeIL              | 7                |

| 30                   | Vcc1                       | $\langle \rangle$ |                      | ResetL                     | 9                |

| 29                   | VccTx<br>Top view of board | $\langle \rangle$ |                      | VccRx                      | 10               |

| 28                   | IntL / RxLOS               |                   | bottom view of board | SCL                        | 11               |

| 27                   | ModPrsI                    |                   |                      | SDA                        | 12               |

| 26                   | GND                        | 1 1               |                      | GND                        | 13               |

| 25                   | RX4p                       |                   |                      | RX3p                       | 14               |

| 24                   | RX4n                       |                   |                      | RX3n                       | 15               |

| 23                   | GND                        |                   |                      | GND                        | 15               |

| 22                   | RX2p                       |                   |                      |                            | 17               |

| 21                   | RX2n                       |                   |                      | RX1p                       |                  |

| 20                   | GND                        |                   |                      | RX1n<br>GND                | 18<br>19         |

|                      |                            | /                 |                      |                            |                  |

Figure 2 QSFP112 Module contact assignment

# QSFP112

# Table 3 QSFP112 Module contact and Host PCB pad electrical definition

| Host    | Module  |                |                  |                                     | Plug     |       |

|---------|---------|----------------|------------------|-------------------------------------|----------|-------|

| PCB pad | contact | Logic          | Symbol           | Description                         | Sequence | Notes |

| 1       |         |                | GND              | Ground                              | 1        | 1     |

| 2       | 1       |                | GND              | Ground                              | 1        | 1     |

| 3       | 2       | CML-I          | Tx2n             | Transmitter Inverted Data Input     | 3        |       |

| 4       | 3       | CML-I          | Tx2p             | Transmitter Non-Inverted Data Input | 3        |       |

| 5       | 4       |                | GND              | Ground                              | 1        | 1     |

| 6       | 4       |                | GND              | Ground                              | 1        | 1     |

| 7       | 5       | CML-I          | Tx4n             | Transmitter Inverted Data Input     | 3        |       |

| 8       | 6       | CML-I          | Tx4p             | Transmitter Non-Inverted Data Input | 3        |       |

| 9       | 7       |                | GND              | Ground                              | 1        | 1     |

| 10      |         |                | GND              | Ground                              | 1        | 1     |

| 11      | 8       | LVTTL-I        | ModSelL          | Select                              | 3        |       |

| 12      | 9       | LVTTL-I        | ResetL           | Reset                               | 3        |       |

| 13      | 10      |                | Vcc Rx           | +3.3 V Power supply receiver        | 2        | 2     |

| 14      | 10      |                | Vcc Rx           | +3.3 V Power supply receiver        | 2        | 2     |

| 15      | 11      | LVCMOS-<br>I/O | SCL              | 2-wire serial interface clock       | 3        |       |

| 16      | 12      | LVCMOS-<br>I/O | SDA              | 2-wire serial interface data        | 3        |       |

| 17      | 13      |                | GND              | Ground                              | 1        | 1     |

| 18      | 13      |                | GND              | Ground                              | 1        | 1     |

| 19      | 14      | CML-O          | Rx3p             | Receiver Non-Inverted Data Output   | 3        |       |

| 20      | 15      | CML-O          | Rx3n             | Receiver Inverted Data Output       | 3        |       |

| 21      | 16      |                | GND              | Ground                              | 1        | 1     |

| 22      | 10      |                | GND              | Ground                              | 1        | 1     |

| 23      | 17      | CML-O          | Rx1p             | Receiver Non-Inverted Data Output   | 3        |       |

| 24      | 18      | CML-O          | Rx1n             | Receiver Inverted Data Output       | 3        |       |

| 25      | 19      |                | GND              | Ground                              | 1        | 1     |

| 26      | 15      |                | GND              | Ground                              | 1        | 1     |

| 27      | 20      |                | GND              | Ground                              | 1        | 1     |

| 28      |         |                | GND              | Ground                              | 1        | 1     |

| 29      | 21      | CML-O          | Rx2n             | Receiver Inverted Data Output       | 3        |       |

| 30      | 22      | CML-O          | Rx2p             | Receiver Non-Inverted Data Output   | 3        |       |

| 31      | 23      |                | GND              | Ground                              | 1        | 1     |

| 32      | 25      |                | GND              | Ground                              | 1        | 1     |

| 33      | 24      | CML-O          | Rx4n             | Receiver Inverted Data Output       | 3        |       |

| 34      | 25      | CML-O          | Rx4p             | Receiver Non-Inverted Data Output   | 3        |       |

| 35      | 26      |                | GND              | Ground                              | 1        | 1     |

| 36      |         |                | GND              | Ground                              | 1        | 1     |

| 37      | 27      | LVTTL-O        | ModPrsL          | Present                             | 3        |       |

| 38      | 28      | LVTTL-O        | IntL/RxLOS       |                                     | 3        |       |

| 39      | 29      |                | Vcc Tx           | +3.3 V Power supply transmitter     | 2        | 2     |

| 40      |         |                | Vcc Tx           | +3.3 V Power supply transmitter     | 2        | 2     |

| 41      | 30      |                | Vcc1             | +3.3 V Power Supply                 | 2        | 2     |

| 42      | 31      | LVTTL-I        | LPMode/Tx<br>Dis | Low Power Mode/optional 1X Disable  | 3        |       |

| 43      | 32      |                | GND              | Ground                              | 1        | 1     |

| 44      | 52      |                | GND              | Ground                              | 1        | 1     |

| 45      | 33      | CML-I          | Тх3р             | Transmitter Non-Inverted Data Input | 3        |       |

| 46      | 34      | CML-I          | Tx3n             | Transmitter Inverted Data Input     | 3        |       |

| 47      | 35      |                | GND              | Ground                              | 1        | 1     |

| 48      | 55      |                | GND              | Ground                              | 1        | 1     |

| 49      | 36      | CML-I          | Tx1p             | Transmitter Non-Inverted Data Input | 3        |       |

QSFP112 Specification Rev. 2.0

# **QSFP112**

|                                                                                                                    | - opeen     |               |               |                                            |                   | _       |

|--------------------------------------------------------------------------------------------------------------------|-------------|---------------|---------------|--------------------------------------------|-------------------|---------|

| 50                                                                                                                 | 37          | CML-I         | Tx1n          | Transmitter Inverted Data Input            | 3                 |         |

| 51                                                                                                                 | - 38        |               | GND           | Ground                                     | 1                 | 1       |

| 52                                                                                                                 | 50          |               | GND           | Ground                                     | 1                 | 1       |

| Note 1: GN                                                                                                         | ID is the s | ymbol for sig | nal and sup   | ply (power) common for the QSFP112 m       | odule. All are co | ommon   |

| within the                                                                                                         | QSFP112     | module and a  | ll voltages a | are referenced to this potential unless ot | herwise noted.    | Connect |

| these directly to the host board signal-common ground plane.                                                       |             |               |               |                                            |                   |         |

| Note 2: Vcc Rx, Vcc1 and Vcc Tx are the receiver and transmitter power supplies and shall be applied concurrently. |             |               |               |                                            |                   |         |

| Requirements, defined for the host side of the Host Edge Card Connector, are listed in Table 4. Recommended        |             |               |               |                                            |                   |         |

| host board power supply filtering is shown in Figure 4. Vcc Rx, Vcc1and Vcc Tx may be internally connected within  |             |               |               |                                            |                   |         |

| the QSFP112 module in any combination. The connector pins are each rated for a maximum current of 1.5A (max.       |             |               |               |                                            |                   |         |

| current of 2.0 A is required for high module power of 15-20W).                                                     |             |               |               |                                            |                   |         |

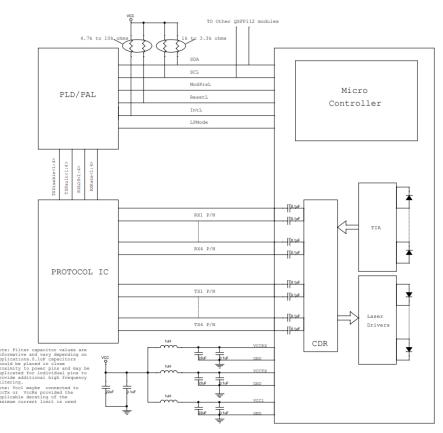

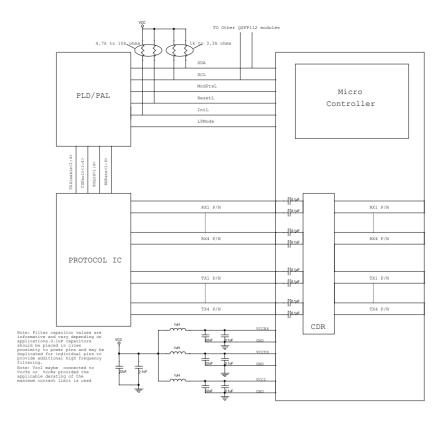

Figure 4, Figure 5 and Figure 6 show example of QSFP host PCB schematic with connections to CDR and control ICs.

Figure 4 Example QSFP112 host board schematic for optical modules

Figure 6 Example QSFP112 host board schematic for passive copper cables

# QSFP[]]2

# 4.1.1 Low Speed Electrical Hardware Pins

In addition to the two wire interface (TWI) serial interface the module has the following low speed pins for control and status:

- a) ModSelL

- b) LPMode/TxDis

- c) ResetL

- d) ModPrsL

- e) IntL/RxLOSL

#### 4.1.1.1 ModSelL

The ModSelL is an input pin. When held low by the host, the module responds to TWI serial communication commands. The ModSelL allows the use of multiple QSFP112 modules on a single TWI bus. When the ModSelL is "High", the module shall not respond to or acknowledge any TWI communication from the host. ModSelL signal input node must be biased to the "High" state in the module.

In order to avoid conflicts, the host system shall not attempt TWI communications within the ModSelL de-assert time after any QSFP112 modules are deselected. Similarly, the host must wait at least for the period of the ModSelL assert time before communicating with the newly selected module. The assertion and de-asserting periods of different modules may overlap as long as the above timing requirements are met.

#### 4.1.1.2 ResetL

The ResetL pin must be pulled to Vcc in the QSFP112 module. A low level on the ResetL pin for longer than the minimum pulse length (t\_Reset\_init) initiates a complete module reset, returning all user module settings to their default state. Module Reset Assert Time (t\_init) starts on the rising edge after the low level on the ResetL pin is released. During the execution of a reset (t\_init) the host shall disregard all status bits until the module indicates a completion of the reset interrupt. The module indicates this by posting an IntL signal with the Data\_Not\_Ready bit negated. Note that on power up (including hot insertion) the module should post this completion of reset interrupt without requiring a reset.

#### 4.1.1.3 LPMode/TxDis

LPMode/TxDis is a dual-mode input signal from the host operating with active high logic. It shall be pulled towards Vcc in the module. At power-up or after ResetL is deasserted LPMode/TxDis behaves as LPMode. If supported, LPMode/TxDis can be configured as TxDis using the TWI except during the execution of a reset. Timing requirements for LPMode/TxDis mode changes are found in, see Table 15. LPMode is used in the control of the module power mode, see CMIS Chapter 6.3.1.3.

When LPMode/TxDis is configured as LPMode, the module behaves as though TxDis=0. By using the LPMode signal and a combination of the Power\_override, Power\_set and High\_Power\_Class\_Enable software control bits the host controls how much power a module can consume. When LPMode/TxDis is configured as TxDis, the module behaves as though LPMode=0. In this mode LPMode/TxDis when set to 1 or 0 disables or enables all optical transmitters within the times specified in Table 15.

Changing LPMode/TxDis mode from LPMode to TxDis when the LPMode/TxDis state is high disables all optical transmitters. If the module was in low power mode, then the module transitions out of low power mode at the same time. If the module is already in high power state (Power Override control bits) with transmitters already enabled, the module shall disable all optical transmitters. Changing the LPMode/TxDis mode from LPMode to TxDis when the LPMode/TxDis state is low, simply changes the behavior of the mode of LPMode/TxDis. The behavior of the module depends on the Power Override control bits.

# QSFP[][]2

Note that the "soft" functions of TxDis, LPMode, IntL and RxLOSL allow the host to poll or set these values over the TWI as an alternative to monitoring/setting signal values. Asserting either the

"hardware" or "soft bit" (or both) for TxDis or LPMode results in that function being asserted. Editor' s Note: registers to support optional TxDis will be added in future revisions of CMIS.

#### 4.1.1.4 ModPrsL

ModPrsL is pulled up to Vcc\_Host on the host board and grounded in the module. The ModPrsL is asserted "Low" when inserted and deasserted "High" when the module is physically absent from the host connector.

#### 4.1.1.5 IntL/RxLOSL

IntL/RxLOSL is a dual-mode active-low, open-collector output signal from the module. It shall be pulled up towards Vcc on the host board (see Table 4). At power-up or after ResetL is released to high, IntL/RxLOSL is configured as IntL. When the IntL signal is asserted Low it indicates a change in module state, a possible module operational fault or a status critical to the host system. The host identifies the source of the interrupt using the TWI serial interface. The IntL signal is deasserted "High" after all set interrupt flags are read. If dual mode operation supported, IntL/RxLOSL can be optionally programmed as RxLOSL using the TWI except during the execution of a reset. If the module has no interrupt flags asserted (IntL/RxLOSL is high), there should be no change in IntL/RxLOSL states after the mode change. If IntL/RxLOSL is configured as RxLOSL, a low indicates that there is a loss of received optical power on at least one lane. "high" indicates that there is no loss of received optical power. Timing requirements for IntL/RxLOSL including fast RxLOS mode are found in Table 15. The actual condition of loss of optical receive power is specified by other governing documents, as the alarm threshold level is application specific. The module shall pull RxLOSL to low if any lane in a multiple lane module or cable has a LOS condition and shall release RxLOSL to high only if no lane has a LOS condition.

Editor' s Note: registers to support optional RxLOSL will be added in future revisions of CMIS.

#### 4.1.2 Low Speed Electrical Specification

Low speed signaling other than SCL and SDA is based on Low Voltage TTL (LVTTL) operating at Vcc. Vcc refers to the generic supply voltages of VccTx, VccRx, Vcc\_host or Vcc1. Hosts shall use a pull-up resistor connected to Vcc\_host on each of the TWI SCL (clock), SDA (data), and all low speed status outputs. The SCL and SDA is a hot plug interface that may support a bus topology. During module insertion or removal, the module may implement a pre-charge circuit which prevents corrupting data transfers from other modules that are already using the bus.

The QSFP112 low speed electrical specifications are given in Table 4. This specification ensures compatibility between host bus masters and the TWI.

# QSFP[]]2

| Parameter                              | Symbol | Min       | Max       | Unit | Condition                                                                    |

|----------------------------------------|--------|-----------|-----------|------|------------------------------------------------------------------------------|

| SCL and SDA                            | VOL    | 0         | 0.4       | v    | IOL(max) = 3.0 mA for<br>fast mode, 20 mA for<br>Fast-mode plus              |

|                                        | VOH    | Vcc - 0.5 | Vcc + 0.3 | V    |                                                                              |

| SCL and SDA                            | VIL    | -0.3      | Vcc*0.3   | V    |                                                                              |

| SCL and SDA                            | VIH    | Vcc*0.7   | Vcc + 0.5 | V    |                                                                              |

| Capacitance for SCL<br>and SDA I/O pin | Ci     |           | 14        | pF   |                                                                              |

| Total bus capacitive load for          | Cb     |           | 100       | pF   | 3.0 k Ohms Pull up<br>resistor, max                                          |

| SCL and SDA                            |        |           | 200       | pF   | 1.6 k Ohms Pull up<br>resistor, max                                          |

| LPMode/TxDis, Reset and<br>ModeSelL    | VIL    | -0.3      | 0.8       | V    | lin   = 125 uA for 0V <<br Vin < Vcc                                         |

| WIOGESCIE                              | VIH    | 2         | VCC + 0.3 | V    |                                                                              |

|                                        | VOL    | 0         | 0.4       | V    | loL= 2.0 mA                                                                  |

| IntL/RxLOS                             | VOH    | VCC - 0.5 | VCC + 0.3 | V    | 10 k ohms pull-up to Host<br>Vcc                                             |

|                                        | VOL    | 0         | 0.4       | V    | loL= 2.0 mA                                                                  |

| ModPrsL                                | VOH    |           |           |      | ModPrsL can be<br>implemented as a short-<br>circuit to GND on the<br>module |

#### Table 4 Low speed control and sense signals

# 4.1.3 High Speed Electrical Specification

#### 4.1.3.1 Rx(n)(p/n)

Rx(n)(p/n) are QSFP112 module receiver data outputs. Rx(n)(p/n) are AC-coupled 100 Ohm differential lines that should be terminated with 100 Ohm differentially at the Host ASIC(SerDes). The AC coupling is inside the QSFP112 module and not required on the Host board. When properly terminated, the differential voltage swing shall be less than or equal to 900 mVpp or the relevant standard, whichever is less.

Output squelch for loss of optical input signal, hereafter Rx Squelch, is required and shall function as follows. In the event of the Rx input signal on any optical port becoming equal to or less than the level required to assert LOS, then the receiver output(s) associated with that Rx port shall be squelched. A single Rx optical port can be associated with more than one Rx output. In the squelched state output impedance levels are maintained while the differential voltage amplitude shall be less than 50 mVpp. In normal operation the default case has Rx Squelch active. Rx Squelch can be deactivated using Rx Squelch Disable through the TWI serial interface. Rx Squelch Disable is an optional function.

# QSFP112

#### 4.1.3.2 Tx(n)(p/n)

Tx(n)(p/n) are QSFP112 module transmitter data inputs. They are AC-coupled 100 Ohm differential lines with 100 Ohm differential terminations inside the QSFP112 optical module. The AC coupling is implemented inside the QSFP112 optical module and not required on the Host board.

Output squelch for loss of electrical signal, hereafter Tx Squelch, is an optional function. Where implemented it shall function as follows. In the event of the differential, peak-to-peak electrical signal amplitude on any electrical input channel becoming less than 70 mVpp, then the transmitter optical output associated with that electrical input channel shall be squelched and the associated TxLOS flag set. If multiple electrical input channels are associated with the same optical output channel, the loss of any of the incoming electrical input channels causes the optical output channel to be squelched.

For applications, e.g. Ethernet, where the transmitter off condition is defined in terms of average power, squelching by disabling the transmitter is recommended and for applications, e.g. InfiniBand, where the transmitter off condition is defined in terms of OMA, squelching the transmitter by setting the OMA to a low level is recommended.

In module operation, where Tx Squelch is implemented, the default case has Tx Squelch active. Tx Squelch can be deactivated using Tx Squelch Disable through the TWI serial interface. Tx Squelch and Tx Squelch Disable are optional functions.

#### **4.2 Power Requirements**

The power supply has three designated pins, Vcc Tx, Vcc1, and Vcc Rx, in the connector. Vcc1 is used to supplement Vcc Tx or Vcc Rx at the discretion of the module vendor. Power is applied concurrently to these pins.

Since different classes of modules exist with pre-defined maximum power consumption limits, it is necessary to avoid exceeding the system power supply limits and cooling capacity when a module is inserted into a system designed to only accommodate lower power modules. It is recommended that the host, through the management interface, identify the power consumption class of the module before allowing the module to go into high power mode.

A host board together with the QSFP112 module(s) forms an integrated power system. The host supplies stable power to the module. The module limits electrical noise coupled back into the host system and limits inrush charge/current during hot plug insertion.

All specifications shall be met at the maximum power supply current. No power sequencing of the power supply is required of the host system since the module sequences the contacts in the order of ground, supply and signals during insertion.

# 4.2.1 Host Board Power Supply Filtering

The host board should use the power supply filtering shown in Figure 7.

#### Figure 7 Recommended host board power supply filtering

Any voltage drop across a filter network on the host is counted against the host DC set point accuracy specification. Inductors with DC Resistance of less than 0.1 Ohm should be used to maintain the required voltage at the Host Edge Card Connector.

The specification for the power supply is shown in Table 5.

| Parameter                                                      | Min | Nominal | Max  | Unit  | Condition                                             |  |

|----------------------------------------------------------------|-----|---------|------|-------|-------------------------------------------------------|--|

| Vcc                                                            |     | 3.3     |      | V     | Measured at Vcc Tx, Vcc Rx and Vcc1.                  |  |

| Vcc set point accuracy                                         | -5  |         | 5    | %     | Measured at Vcc Tx, Vcc Rx and Vcc1.                  |  |

| Power Supply Noise<br>including ripple                         |     |         | 50   | mV    | 1 kHz to frequency of operation measured at Vcc_host. |  |

| Module Maximum Current<br>Inrush with LPMode Pin<br>asserted   |     |         | 0.55 | A     |                                                       |  |

| Module Maximum Current<br>Inrush with LPMode Pin<br>deasserted |     |         | 1.3  | A     |                                                       |  |

| Module Current Ramp Rate                                       |     |         | 100  | mA/uS |                                                       |  |

#### Table 5 Power supply specification

#### 4.2.2 Power Classes and Maximum Power Consumption

Power levels associated with classifications of module are shown in Table 6.

Since a wide range of module power classes exist, to avoid exceeding the system power supply limits and cooling capacity when a module is inserted into a system designed to accommodate only low power consumption modules, it is recommended that host systems designed to accommodate only low power consumption modules also implement the state machine defined in the CMIS or SFF-8636 and identify the power class of the module before allowing the module to go into High Power Mode, where power class 8 requires reading CMIS, Page00, Byte 201 to determine actual power consumption. This is to avoid exceeding the host system power supply limits and cooling capacity when a module exceeding the power class supported by the system is inserted.

| Power Class                                                                             | Max Power (W) | CMIS Register                                 |  |  |  |

|-----------------------------------------------------------------------------------------|---------------|-----------------------------------------------|--|--|--|

| 1                                                                                       | 1.5           | Direct readout of Page 00h Byte 200[000xxxxx] |  |  |  |

| 2                                                                                       | 2.0           | Direct readout of Page 00h Byte 200[001xxxxx] |  |  |  |

| 3                                                                                       | 2.5           | Direct readout of Page 00h Byte 200[010xxxxx] |  |  |  |

| 4                                                                                       | 3.5           | Direct readout of Page 00h Byte 200[011xxxxx] |  |  |  |

| 5                                                                                       | 4.0           | Direct readout of Page 00h Byte 200[100xxxxx] |  |  |  |

| 6                                                                                       | 4.5           | Direct readout of Page 00h Byte 200[101xxxxx] |  |  |  |

| 7                                                                                       | 5.0           | Direct readout of Page 00h Byte 200[110xxxxx] |  |  |  |

| 8 <sup>1</sup>                                                                          | >5.0          | Direct readout of Page 00h Byte 200[111xxxxx] |  |  |  |

| Note: 1. When a module reports power class 8, the host must read CMIS Page 00h Byte 201 |               |                                               |  |  |  |

| to determine module power dissipation.                                                  |               |                                               |  |  |  |

#### **Table 6 Power budget classification**

In general, the higher power classification level is associated with higher data rates and longer reach. The system designer is responsible for ensuring that the maximum temperature does not exceed the case temperature requirements.

During hot-plug, power cycle or reset, all QSFP112 modules shall power up in Low Power Mode if LPMode is asserted to avoid exceeding the host system power capacity. If LPMode is not asserted, the module will proceed to High Power Mode without host intervention. Figure 8 shows waveforms for maximum instantaneous, sustained and steady state currents for Low Power and High Power modes.

Figure 8 Instantaneous and sustained peak currents for icc host

Specification values for maximum instantaneous, sustained and steady state currents at each power class are given in Table 7. The module shall not be affected by the instantaneous variations of the power supply caused by its own current drawing profile during all power transient events.

| Parameter                                                            | Symbol        | Min   | Nom     | Max                 | Unit   |

|----------------------------------------------------------------------|---------------|-------|---------|---------------------|--------|

| Power supply voltages VccTx, VccRx, including                        |               | 3.135 | 3.3     | 3.465               | V      |

| ripple, droop and noise below 100 kHz <sup>1</sup>                   |               | 5.155 | 5.5     | 5.405               | v      |

| Module inrush - instantaneous peak duration <sup>2</sup>             | T_ip          |       |         | 50                  | μs     |

| Module inrush - initialization time <sup>2</sup>                     | T_init        |       |         | 500                 | ms     |

| Power Class 1 module and Low Power Mode for                          | other module  | S     |         |                     |        |

| Power Consumption                                                    | P_lp          |       |         | 1.5                 | W      |

| Instantaneous peak current at hot plug                               | lcc_ip_lp     | -     | -       | 600                 | mA     |

| Sustained peak current at hot plug                                   | lcc_sp_lp     | -     | -       | 495                 | mA     |

| Steady state current                                                 | lcc_lp        |       | See No  | te 3                | mA     |

| High Power Mode Power Class 2 module                                 |               |       |         |                     |        |

| Power Consumption                                                    | P_2           |       |         | 2.0                 | W      |

| Instantaneous peak current                                           | lcc_ip_2      | -     | -       | 800                 | mA     |

| Sustained peak current                                               | lcc_sp_2      | -     | -       | 660                 | mA     |

| Steady state current                                                 | Icc 2         |       | See No  | te 3                | mA     |

| High Power Mode Power Class 3 module                                 |               |       |         |                     |        |

| Power Consumption                                                    | P 3           |       |         | 2.5                 | W      |

| Instantaneous peak current                                           | lcc_ip_3      | -     | -       | 1000                | mA     |

| Sustained peak current                                               | lcc_sp_3      | -     | -       | 825                 | mA     |

| Steady state current                                                 | Icc 3         |       | See No  |                     | mA     |

| High Power Mode Power Class 4 module                                 | _ · · · · _ · |       |         |                     |        |

| Power Consumption                                                    | P 4           |       |         | 3.5                 | W      |

| Instantaneous peak current                                           | lcc_ip_4      | -     | -       | 1400                | mA     |

| Sustained peak current                                               | lcc_sp_4      | -     | -       | 1155                | mA     |

| Steady state current                                                 | lcc 4         |       | See No  |                     | mA     |

| High Power Mode Power Class 5 module                                 |               |       | 000.10  |                     |        |

| Power Consumption                                                    | P 5           |       |         | 4.0                 | W      |

| Instantaneous peak current                                           | Icc ip 5      | -     | -       | 1600                | mA     |

| Sustained peak current                                               | lcc_sp_5      | -     | -       | 1320                | mA     |

| Steady state current                                                 | lcc 5         |       | See No  |                     | mA     |

| High Power Mode Power Class 6 module                                 |               |       |         |                     |        |

| Power Consumption                                                    | P 6           |       |         | 4.5                 | W      |

| Instantaneous peak current                                           | lcc_ip_6      | -     | -       | 1800                | mA     |

| Sustained peak current                                               | lcc_sp_6      | -     | -       | 1485                | mA     |

| Steady state current                                                 |               |       | See No  |                     | mA     |

| High Power Mode Power Class 7 module                                 |               |       | 500 110 |                     | 1117 ( |

| Power Consumption                                                    | P 7           |       |         | 5                   | W      |

| Instantaneous peak current                                           | lcc_ip_7      | -     | -       | 2000                | mA     |

| Sustained peak current                                               | lcc_sp_7      | _     | _       | 1650                | mA     |

| Steady state current                                                 | $lcc_{3p_1}$  |       | See No  |                     | mA     |

| High Power Mode Power Class 8 module                                 | 100_1         |       | JUCINU  |                     |        |

| Power Consumption                                                    | P 8           |       |         | > 5                 | W      |

| Instantaneous peak current                                           | Icc ip 8      | -     | -       | P 8/2.5             | A      |

| Sustained peak current                                               | lcc_sp_8      |       |         | P_0/2.5<br>P 8/3.03 | A      |

|                                                                      |               | +     | - 6.0   | r_0/3.03            |        |

| Steady state current<br>Notes: 1. Measured at VccTx, VccRx and Vcc1. | lcc_8         | 1     | 0.0     |                     | A      |

#### Table 7 QSFP112 Module power supply specification

2: T\_ip and T\_init are test conditions for measuring inrush current and not characteristics of the module.

3: The module must stay within its declared power class.

4: P\_8 is the module power dissipation reported by CMIS Byte 201.

# QSFP[][]2

# 4.3 ESD

The module and all pins shall withstand 500V electrostatic discharge based on Human Body Model per JEDEC JESD22-A114-B.

The module shall meet ESD requirements given in EN61000-4-2, criterion B test specification such that when installed in a properly grounded cage and chassis the units are subjected to 15KV air discharges during operation and 8KV direct contact discharges to the case.

# **5** Mechanical and Board Definition

#### 5.1 Introduction

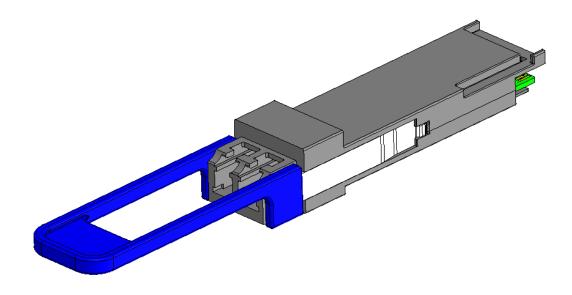

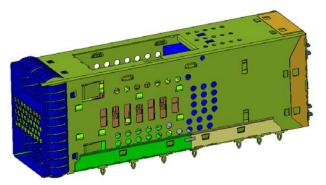

The overall module defined in this clause is illustrated in Figure 9. The module and connector dimensions described in this clause are constant for all applications. The bezel, cage assembly, heat sink can be designed and/or adjusted for the individual application.

#### Figure 9 QSFP112 Module rendering

#### 5.2 QSFP112 Datums and Component Alignment

A listing of the datums for the various components is contained in Table 8. The alignments of some of the datums are noted. The relationship of the Module, Cage, and Connector relative to the Host Board and Bezel are illustrated in Figure 10 and Figure 11 by the location of the key datums of each of the components. In order to reduce the complexity of the drawings, all dimensions are considered centered unless otherwise specified.

# **QSFP112**

# Table 8 Definition of datums

| Datum          | Description                                                     |

|----------------|-----------------------------------------------------------------|

| А              | Top surface of Host Board                                       |

| В              | Inside surface of bezel                                         |

| С              | Distance between connector terminal through holes on host board |

| D              | Hard stop on module                                             |

| E              | Width of module                                                 |

| F              | Height of module housing                                        |

| G              | Width of PCB                                                    |

| н              | Leading edge of signal contact pads on PCB                      |

| J              | Top surface of PCB                                              |

| к              | Host Board through hole #1 to accept contact guide post         |

| L              | Host Board through hole #2 to accept contact guide post         |

| Р              | Centerline of cage width                                        |

| R              | Centerline of cage height                                       |

| S              | Seating plane of cage on host board                             |

| т              | Hard stop on cage                                               |

| W              | Seating surface of the heat sink on the cage                    |

| х              | Host board through hole #1 to accept cage pin                   |

| Z              | Width of heat sink surface that fits into clip                  |

| AA             | Connector slot width                                            |

| BB             | Seating plane of connector on host board                        |

| DD             | Top surface of module housing                                   |

| Notes:<br>1. [ | Datums D, K, L, N and T are aligned when assembled              |

2. Centerlines of datums AA,C,E,G,M,P and Z are aligned on the same vertical axis

Figure 10 QSFP112 1X1 SMT Connector/Cage/Module Datum

# 5.3 QSFP112 Module Mechanical Package Dimensions

#### 5.3.1 Module Form Factors

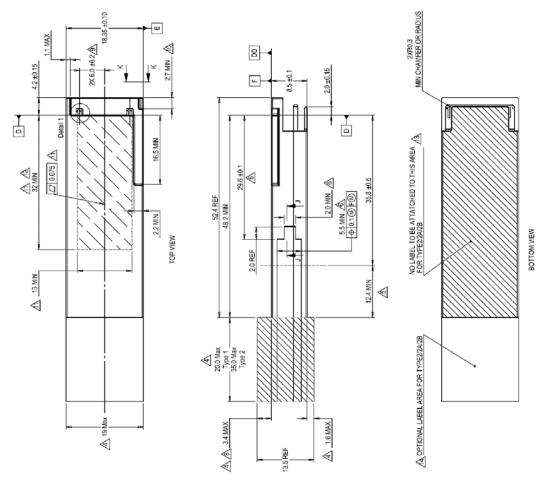

A common mechanical outline is used for all QSFP112 modules. The shell provides a means to self-lock with the cage upon insertion. The package dimensions for the QSFP112 module are defined in Figure 12 and Figure 13. The dimensions that control the size of the module that extends outside of the cage are listed as maximum dimensions per below Note 4 and Note 8 in Figure 12.

NOTES APPLY TO MODULE DRAWING

- 1. DIMENSIONS AND TOLERANCING CONFORM TO ASME Y14.5-2009.

- 2. ALL DIMENSIONS ARE IN MILLIMETERS.

- 3. UNLESS OTHERWISE SPECIFIED, SHARP CORNERS, EDGES, AND BURRS ARE NOT ALLOWED. ROUND OFF ALL EDGES AND CORNERS TO A MINIMUM RADIUS OF 0.2MM.

- 4. DIMENSIONS DEFINES ENLARGED SECTION OF TRANSCEIVER THAT EXTENDS OUTSIDE OF CAGE TO ACCOMMODATE MATING PLUG AND ACTUATOR MECHANISM.

- 5. SURFACES ON ALL 4 SIDES OF THE 12.4 MIN DIMENSION TO BE CONDUCTIVE FOR CONNECTION TO CHASSIS GROUND.

- 6. DIMENSION APPLIES TO LATCH MECHANISM.

- 7. DIMENSION APPLIES TO THE LOCATION OF THE EDGE OF THE MODULE BOARD PAD, DATUM H. CONTACTS 21, 22, 36, AND 37 ARE VISIBLE.

- 8. DIMENSION TO INCLUDE BAIL TRAVEL.

- 9. DIMENSION APPLY TO OPENNINGS IN THE HOUSING.

- 10. FEATURE MAY BE LONGER THAN SHOWN.

- 11. FLATNESS AND SURFACE ROUGHNESS (Ra) APPLIES FOR INDICATED LENGTH AND MIN WIDTH OF 13MM. SURFACE TO BE THERMALLY CONDUCTIVE. SEE SECTION 5.3.2 TABLE 9 FOR FLATNESS AND ROUGHNESS REQUIREMENS.

- 12. HIGH WATTAGE MODULES MAY REQUIRE ADDITIONAL SPACE FOR COOLING.

- 13. NO LABEL SHALL BE APPLIED IN THIS AREA FOR TYPE 2/2A/2B. ETCHINGS ARE ALLOWED BUT MUST NOT AFFECT THERMAL PERFORMANCE.

- 14. THE LABEL(S) MUST NOT INTERFERE WITH THE MECHANICAL, THERMAL, OR EMI PERFORMANCE AND MUST NOT VIOLATE NOTE 5.

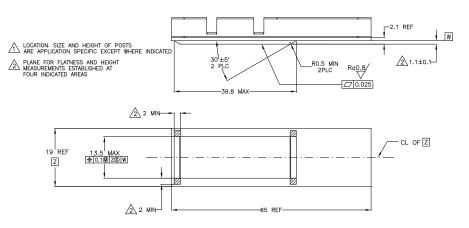

Figure 12 Drawing of QSFP112 module (Part 1 of 2)

Figure 13 Drawing of QSFP112 module (Part 2 of 2)

# 5.3.2 Module Flatness and Roughness

QSFP112 module flatness and roughness are specified to improve module thermal characteristics when used with a riding heat sink. Relaxed specifications are used for lower power modules to reduce cost. The module flatness and roughness specifications apply to the specified heat sink contact area for QSFP112 by Figure 12 and Figure 13. Specifications for QSFP112 Module flatness and surface roughness are shown in Table 9. Flatness and roughness specifications applies to both top and bottom surfaces of the modules. Power class 1Cu is dedicated to passive copper cables with a more relaxed flatness of 0.15 mm.

| Power Class <sup>1</sup>                         | Module Flatness (mm) | Surface Roughness (Ra, µm) |  |  |  |

|--------------------------------------------------|----------------------|----------------------------|--|--|--|

| 1Cu <sup>2</sup>                                 | 0.15                 | 1.6                        |  |  |  |

| 1                                                | 0.075                | 1.6                        |  |  |  |

| 2                                                | 0.075                | 1.6                        |  |  |  |

| 3                                                | 0.075                | 1.6                        |  |  |  |

| 4                                                | 0.075                | 1.6                        |  |  |  |

| 5                                                | 0.075                | 1.6                        |  |  |  |

| 6                                                | 0.075                | 1.6                        |  |  |  |

| 7                                                | 0.075                | 1.6                        |  |  |  |

| 8                                                | 0.050                | 0.8                        |  |  |  |

| 1. QSFP112 power classes are defined in Table 6. |                      |                            |  |  |  |

#### Table 9 QSFP112 Module flatness specifications

Power class 1Cu maximum power dissipation is the same as power class 1.

# 5.3.3 Mating of QSFP112 Module PCB to QSFP112 Electrical Connector

The pad definition data is generic for high speed datacom applications such as Fiber Channel, Ethernet and SONET/ATM.

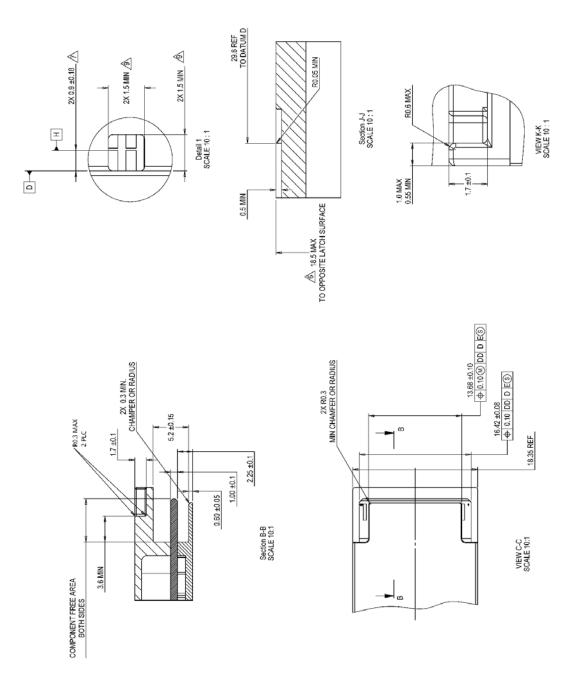

To support 112 Gb/s serial data rates the QSFP112 module paddle card pad dimensions have been modified. See Figure 14 for QSFP112 module updated paddle card pad dimensions, which uses 0.45 mm in width and 1.4mm in length. All other module dimensions, except for the pads, remain the same as the QSFP+/QSFP28 specifications.

# QSFP1112

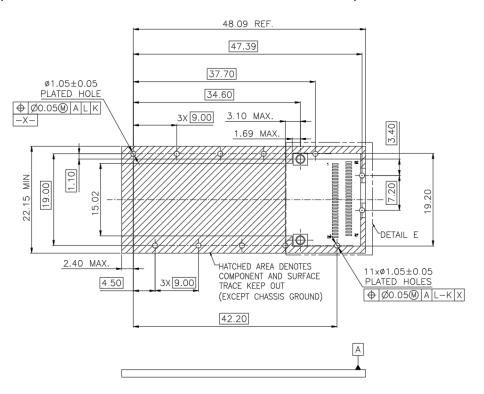

#### 5.4 Host PCB Layout

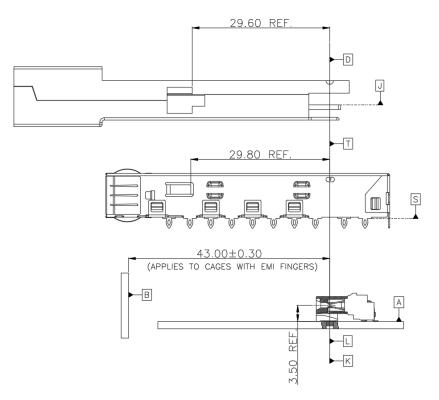

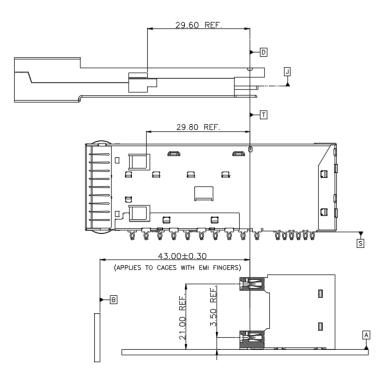

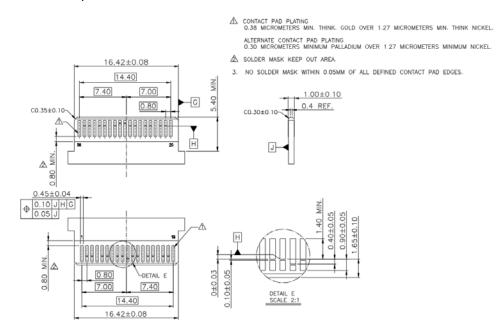

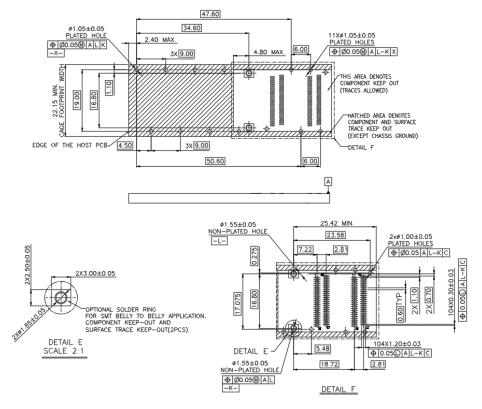

A typical host board mechanical layout of single mount for attaching the QSFP112 Connector and Cage System is shown in Figure 15, Figure 16, Figure 17, Figure 18 and Figure 19, the connector and the cage can also support belly to belly application of host board. Location of the pattern on the host board is application specific. See Clause 4.6 for details on the location of the pattern relative to the bezel.

Figure 15 QSFP112 1x1 SMT Connector and cage PCB layout

# **QSFP112**

Figure 17 QSFP112 2X1 SMT Connector and cage PCB layout

#### QSFP112 Specification Rev. 2.0

# **QSFP112**

$\bigtriangleup$  There are two types of digital ground design, 0.50mm diameter and 0.82 diameter, and it is up to the user to decide whether to design both diameters on the PCB, or either one.

Figure 19 QSFP112 Qpath112 2X1 Connector and cage PCB layout

# 5.4.1 Insertion, Extraction and Retention Forces for QSFP112 Module

QSFP112 module and cage system insertion, extraction, and retentions forces are given in Table 10. QSFP 112 connector and cage retention system are designed to withstand excessive force applied through the module or cable. The general requirement as applied to the values in the table is that no functional damage shall occur to the module, connector or cage.

| Measurement                                           | Min | Max | Units  | Comments                                                                                    |

|-------------------------------------------------------|-----|-----|--------|---------------------------------------------------------------------------------------------|

| QSFP112 module extraction                             | 0   | 30  | Ν      | EIA-364-13<br>Test with connector, cage and module.<br>(Latch disengaged, without heatsink) |

| QSFP112 module insertion                              | 0   | 60  |        | EIA-364-13<br>Test with connector, cage and module.<br>(Latch disengaged, without heatsink) |

| QSFP112 module retention                              | 90  | NA  | Ν      | No functional damage to module connector or cage                                            |

| Cage retention (Latch strength)                       | 125 | NA  | Ν      | No functional damage to module latch below 125N                                             |

| Cage retention in Host Board                          | 114 | NA  | Ν      | Force to be applied in a vertical direction, no damage to cage                              |

| Insertion and removal cycles of<br>connector and cage | 100 | NA  | Cycles | The durability of QSFP112 connector and cage                                                |

| Insertion and removal cycles of<br>QSFP112 Module     | 50  | NA  | Cycles | The durability of QSFP112 module                                                            |

#### Table 10 Insertion, extraction and retention forces for an QSFP112 module

# QSFP[]]2

#### 5.5 Module Color Coding and Labeling

An exposed feature of the QSFP 112 module (a feature or surface extending outside of the bezel) shall be color coded as follows:

Beige for 850nm Blue for 1310nm White for 1550nm

Each QSFP112 module shall be clearly labeled. The complete labeling need not be visible when the QSFP 112 module is installed. The bottom of the device is the recommended location for the label. Labeling shall include:

Appropriate manufacturer and part number identification

Appropriate regulatory compliance labeling

A manufacturing traceability code

The label should also include clear specification of the external port characteristics such as:

Optical wavelength Required fiber characteristics (i.e. MMF/SMF) Operating data rate Interface standards supported Link length supported Connector Type

The labeling shall not interfere with the mechanical, thermal or EMI features.

#### 5.6 Bezel for Systems Using QSFP112 Modules

Host enclosures that use QSFP112 devices should provide appropriate clearances between the QSFP112 modules to allow insertion and extraction without the use of special tools and a bezel enclosure with sufficient mechanical strength. See Figure 12 for the recommended bezel designs. The recommended host board thickness for belly-to-belly mounting of the assemblies is 2.2mm minimum.

Applications with host boards less than 2.2 mm minimum will require module dimensions of less than 1.6 mm shown with Note 1 of Figure 12.

The front surface of the cage assembly passes through the bezel. If EMI spring fingers are used, they make contact to the inside of the bezel cutouts. If an EMI gasket is used, it makes contact to the inside surface of the bezel. To accept all cage designs, both bezel surfaces must be conductive and connected to chassis ground.

The recommended basic dimension from the bezel centerline to Datum K and Datum L (See Figure 6 and Figure 12) on the Host board is 43.8mm nominal. The total tolerance can be calculated as follows:

+/- tolerance = 1/2 (bezel thickness) + 0.3mm

For example, a bezel thickness of 1.6mm will have a bezel centerline tolerance of +/- 1.1mm.

The dimension of 43.8 +/- 1.1mm would apply from the Centerline of the bezel to Datums K and L. The QSFP112 module insertion slot should be clear of nearby moldings and covers that might block convenient access to the latching mechanisms, the QSFP112 module, or the cables connected to the

QSFP112 module.

#### Figure 20 QSFP112 1X1 SMT and Qpath112 Bezel opening

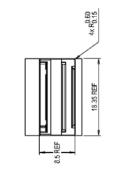

# 5.7 QSFP112 Electrical Connector Mechanical

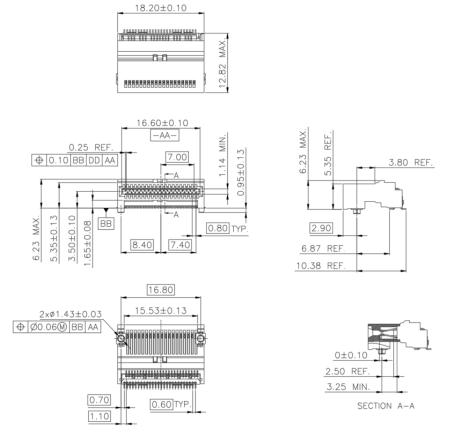

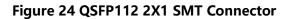

The QSFP112 Connector is a 38-contact, right angle surface mount connector and is shown in Figure 22. The mechanical specification for the connector is shown in Figure 23 and Figure 24.

Figure 22 QSFP112 Module electrical connector illustration

# QSFP112 Specification Rev. 2.0

# **QSFP112**

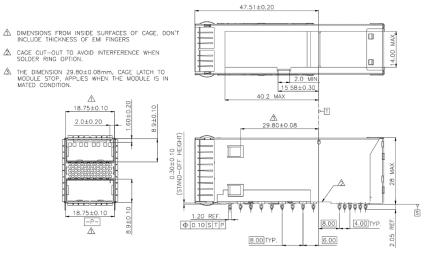

#### Figure 23 QSFP112 1X1 SMT Connector

# 5.8 QSFP112 Cage Assembly

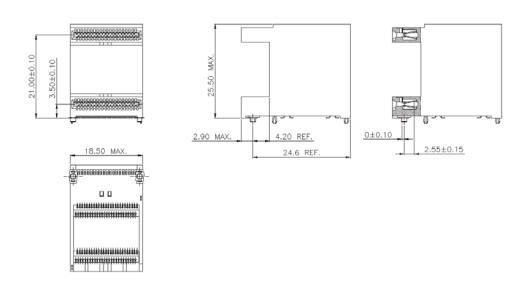

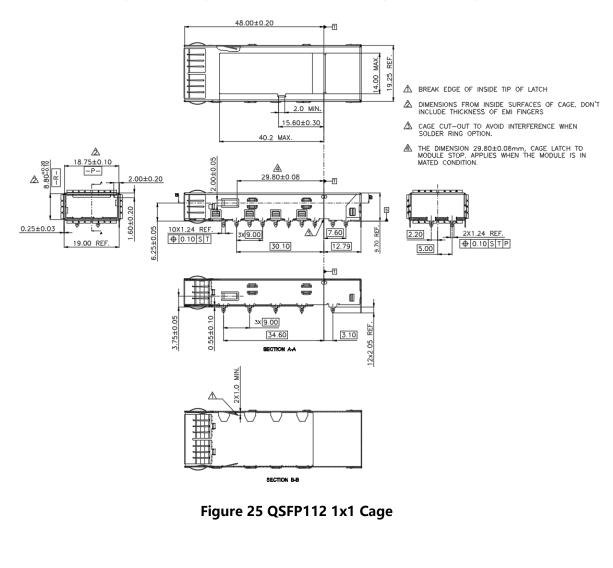

The detailed drawings for the cage assembly are shown in Figure 25 and Figure 26.

Figure 26 QSFP112 2X1 Cage

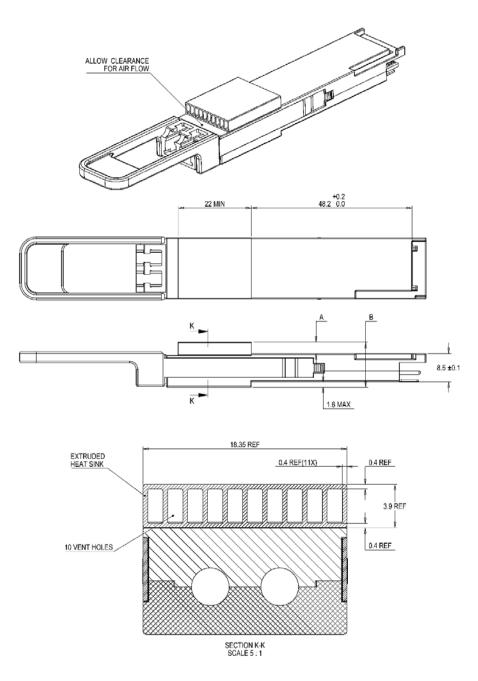

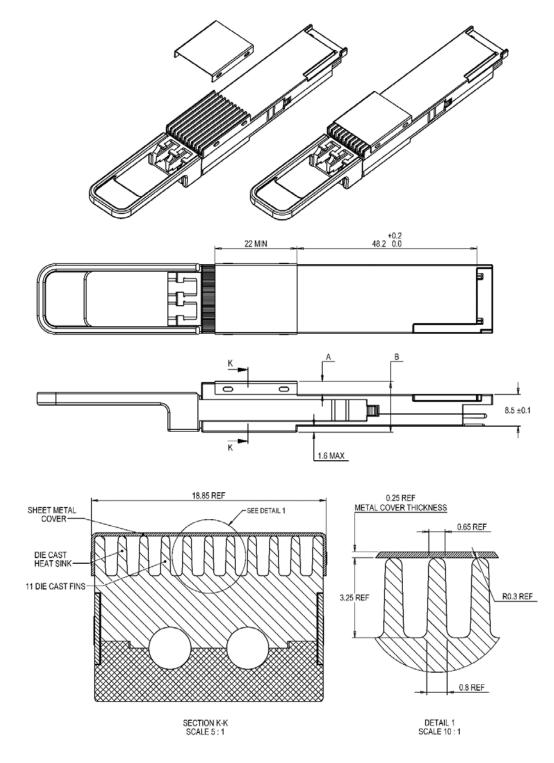

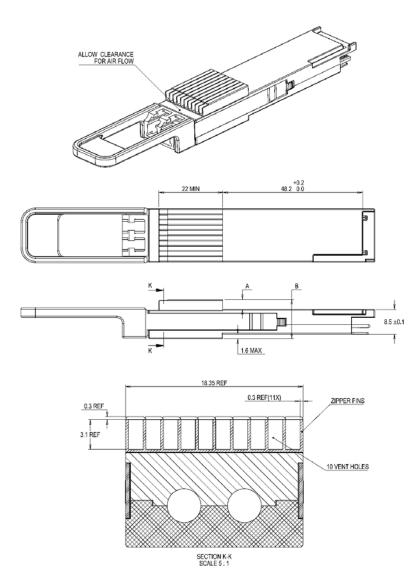

### 5.8.1 QSFP112 Heatsink dimensions

The heat sink illustrated in Figure 27 is for reference only.

Figure 27 QSFP112 Heatsink

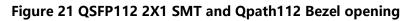

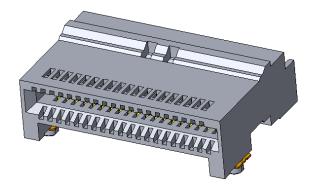

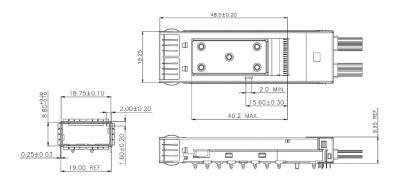

### 5.9 QSFP112 Qpath112 Connector and cage

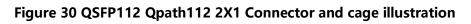

The QSFP112 Qpath112 connector and cage is a 38-contact connector and cage containing high-speed signal contacts that are ultimately connected to cables and low speed and power contacts that are pressed fit to the PCB. The detailed drawings for the Qpath112 connector and cage are shown in Figure 28, Figure29, Figure30 and Figure 31.

Figure 28 QSFP112 Qpath112 1X1 Connector and cage illustration

Figure 29 QSFP112 Qpath112 1X1 Connector and cage

Figure 31 QSFP112 Qpath112 2X1 Connector and cage

## 5.10 Optical Port Mapping and Optical Interfaces

### 5.10.1 Electrical data input/output to optical port mapping

The QSFP112 with 4 transmit lanes [Tx1-Tx4] and 4 receive lanes [Rx1-Rx4] allows optical port mapping as shown in Table 11.

|                 | Optical port mapp | ing (see Figure 32) |

|-----------------|-------------------|---------------------|

| Electrical data | Duplex LC         | MPO-12              |

| input/output    | 1 TX fiber        | 4 TX fibers         |

|                 | 1 RX fiber        | 4 RX fibers         |

| Tx1             |                   | Tx-1                |

| Tx2             | Tx-1              | Tx-2                |

| Tx3             | 12-1              | Tx-3                |

| Tx4             |                   | Tx-4                |

| Rx1             |                   | Rx-1                |

| Rx2             | Dy 1              | Rx-2                |

| Rx3             | Rx-1              | Rx-3                |

| Rx4             |                   | Rx-4                |

### Table 11 Electrical Signal to Optical Port Mapping

### 5.10.2 Optical Interfaces

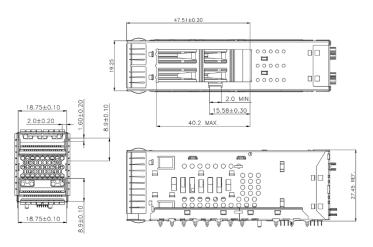

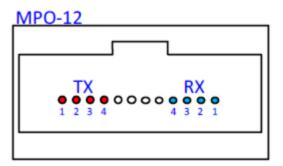

The recommended location and numbering of the optical ports for 3 Media Dependent Interfaces (MDI) are shown in Figure 32. The transmit and receive optical lanes shall occupy the positions depicted in Figure 32 when looking into the MDI receptacle with the connector keyway feature on top. QSFP112 optical MDI examples are shown for a male MPO receptacles (see Figure 33) and a dual LC (see Figure 34).

Figure 32 Optical media dependent interface port assignments

# QSFP112

#### 5.10.2.1 MPO Optical Cable connections

The optical plug and receptacle for the MPO-12 connectors are specified in TIA-604-5 and shown in Figure 33 (MPO-12 Single Row).

Aligned keys are used to ensure alignment between the modules and the patch cords. The optical connector is orientated such that the keying feature of the MPO receptacle is on the top. Note: Two alignment pins are present in each receptacle.

#### Figure 33 MPO-12 One row optical patch cord and module receptacle

#### 5.10.2.2 Dual LC Optical Cable connection

The Dual LC optical patchcord and module receptacle is specified in TIA-604-10 and shown in Figure 34.

Figure 34 Dual LC optical patchcord and module receptacle

# 6 Environmental and Thermal

### 6.1 Temperature Classes

The QSFP112 module shall operate within one or more of the case temperatures ranges defined in Table 12 (a) / Table 12(b). The temperature ranges are applicable between 60m below sea level and 1800m above sea level, (Ref. NEBS GR-63) utilizing the host systems designed airflow.

| Class      | Case Temperature Range |

|------------|------------------------|

| Standard   | 0 through 70°C         |

| Extended   | -5 through 85°C        |

| Industrial | -40 through 85°C       |

#### Table 12 (a) Temperature classification of module case

| Table 12 (b) | Temperature range      | classes for tic | ahter controlled  | applications |

|--------------|------------------------|-----------------|-------------------|--------------|

|              | i chipciului c i ulige |                 | ginter controlled | applications |

| Class | Functional Case<br>Temperature | Case Temperature |

|-------|--------------------------------|------------------|

| A1    | 15 - 60°C                      | 25 - 60°C        |

| A2    | 5 - 60°C                       | 15 - 60°C        |

| A3    | 5 - 70°C                       | 15 - 70°C        |

| A4    | 5 - 75°C                       | 15 - 75°C        |

### 6.2 Informative Thermal Design

QSFP112 is designed to allow for up to 16 adjacent modules, ganged and/or belly-to-belly, with the appropriate thermal design for cooling / airflow. (Ref. NEBS GR-63)

For module dimensions all remain the same as the QSFP+/QSFP28 specifications except for the nose protrusion outside of the faceplate of the equipment, Figure 35 shows the four variants of the QSFP112 modules. Type 1 being consistent with the QSFP28 mechanicals and Type 2 having a longer extension beyond the faceplate that module manufacturers can take advantage of for extra design room internal to the module. Type 2A is a further variant on Type 2 which has an integrated heatsink on the nose of the module to facilitate cooling with an efficient secondary heat transfer path. Type 2B increases the height of the nose heatsink to handle higher module power consumption up to 25W. All module variants are compatible with the common QSFP112 connector and cage designs and can be intermixed in a deployment. The main differences listed below.

- Type 1 (same as QSFP28) 72.4 mm max module length

- Type 2 (type1 + 15mm) 87.4mm max module length

- Type 2A (type2 + normal heat sink)

- Type 2B (type2 + enhanced heat sink)

### Figure 35 QSFP112 Module variants: Type 1; Type 2; Type 2A; and Type 2B